采用Magma Finesim的NAND闪存仿真战略

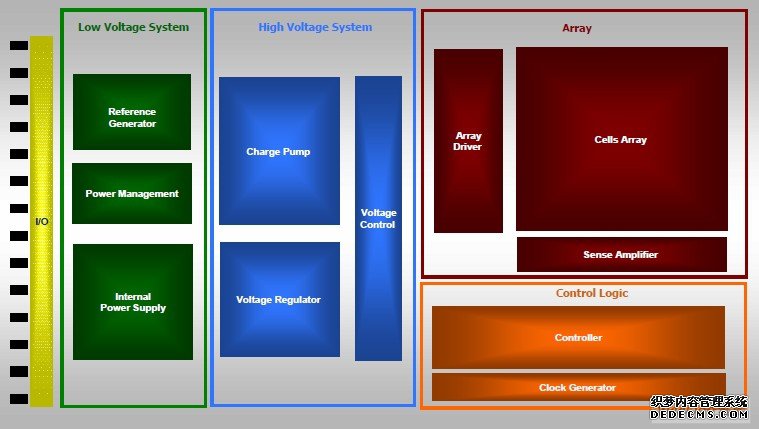

NAND闪存是一种高密度非易失性存储器,基于电压调制原理而操纵。随着技术开发和工艺改进,MLC NAND(2 bit/cell NAND)的架构正变得日益复杂化。今天,单个8Gb密度SLC NAND闪存芯片的MOSFET数目就超过70万,这还未包括所有阵列器件在内;MLC约是SLC的1.5-2倍。图1显示了NAND功能块基本结构图,它通常是由I/O、低压(LV)系统、高压(LV)系统、控制逻辑和阵列5大部分组成。

I/O是芯片接口,包括高速I/O接口电路和ESD。

低压(LV)系统将提供内部电源供给和各个区域的功耗治理。同时它还可产生芯片中其它电路的电压和电流基准。

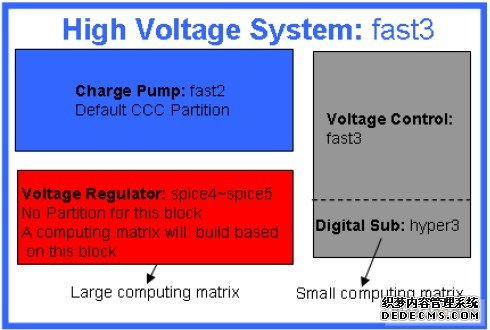

高压(HV)系统是由大量电荷泵、调节器和电压控制电路组成,可为NAND单元提供必要的高电压。

阵列是由单元阵列、阵列驱动器和感知放大器组成;由于其密度巨大,因此它是整个芯片的最大组成部分。

图1 NAND功能块简图

控制逻辑是NAND的最后一个组成部分;它是NAND的大脑,包括有一个智能控制器和一个精密时钟天生器。

要处理全芯片混合信号仿真,我们首先得*估电路规模、仿真所需的整体瞬态分析时间以及我们预期的精度;接着,我们再通过权衡考虑,做出选择。若是要求高的精度,那么我们必须压缩电路规模或缩短瞬态分析时间;相对地,若是要求长的瞬态分析时间或大型电路,那么就只能牺牲精度;否则仿真时间将很长,会影响产品进度。.

在进行NAND闪存仿真时,我们将面对什么?传统规则仍行得通吗?看起来并不。

首先,NAND中实施的混合信号仿真是为了检查所有LV/HV电路是否能与数字部分良好协作、单元运作所需的所有各种高压是否能正确提供。因此,多数HV/LV电路都有高精度需求。

其次,NAND的运作周期从几百微秒至几千微秒不等。例如:一个编程周期约为250微秒,而一个擦写周期则可能约要1.5毫秒。此外,用于控制器或电荷泵的内部时钟周期仅为60-70纳秒左右。这意味着约4,200次时钟周期才能完成一次编程操纵。遗憾的是,在这种操纵中,即便多数电荷泵、调节器、HV开关会不断打开/封闭,那些操纵行为和电压值仍有待具体观察。因此,没什么机会缩短仿真瞬态时间。

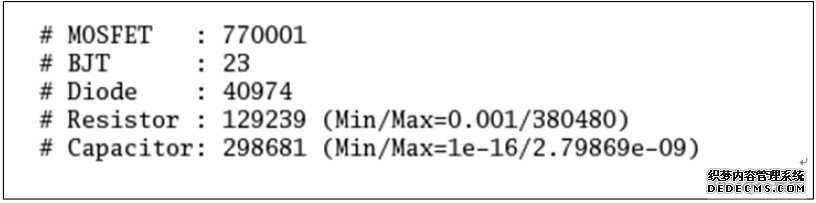

最后,有关电路规模,如图2所列是从一个已减少单元阵列的NAND芯片的网表中所提取的数字。这已是我们必须提交给仿真器的最小值,尽管它还是很大。

图2: 一个减少了单元阵列NAND闪存器件数

大量电荷泵、调节器、电压控制和时钟振荡器的高精度,再加上长的仿真瞬态时间和大的电路规模,所有这些都使得传统混合信号仿真器难以完成NAND仿真。而且看起来似乎‘等待’是唯一的解决途径。

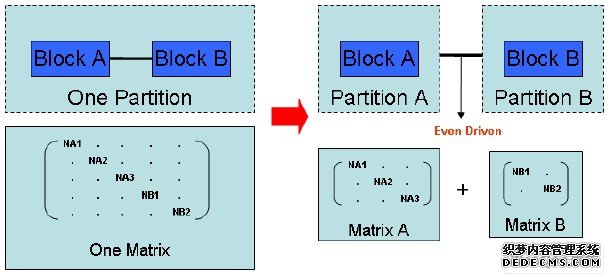

那么,采用Magma Finesim会怎样呢?首先,通过Fast-Spice仿真器引进分区功能,将大电路分为多个小电路。接着,计算矩阵将根据分区,把大矩阵转换为几个相对小的矩阵,从而节省大量计算时间。

图3:采用分区功能的矩阵

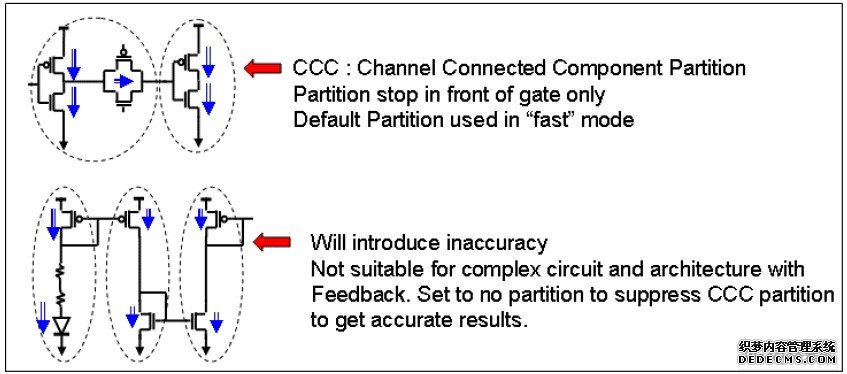

从无分区到CCC分区再到集中型分区(分区工作可SUBCKT边界为终点层次化进行,只适用于逻辑电路),计算矩阵将被分得越来越小。终极,通过对单独功能块进行适当分区设置,我们能够获得一个性能公道、速度可接受的仿真结果。

图4:标准CCC分区

适当分区对大型混合信号芯片的仿真至关重要。下面将以一个典型NAND闪存全芯片仿真为例来描述这种分区战略。

为单独功能块定制精度设置一般而言,不同功能块精度的设置是根据以下全芯片检查中指导而指定:

1) 在最高层,设置一个速度相对快的标准精度,特别是假如主块是逻辑电路时更要如此。

2) 最大程度减少有高精度需求的功能块的数目。例如:模拟和时序关键电路。

3) 对于有高精度要求的模拟块,指定模拟电路核心所在位置中较低水平的设置。

遵从以上指示,我们就能够避免由高精度设置的大功能块形成的大型计算矩阵。

例如:Magma FINESIM高压系统设置如图5所示。在NAND闪存芯片中,高压系统、内部电压天生器的最关键电路均是大型复杂功能块。确保每个模拟电路均能输出预期电压并满足速度要求是最重要一个功能性检查。为了确保这个部分仿真性能良好,我们应对每个单独功能块进行专门设置。

图5 高压系统设置

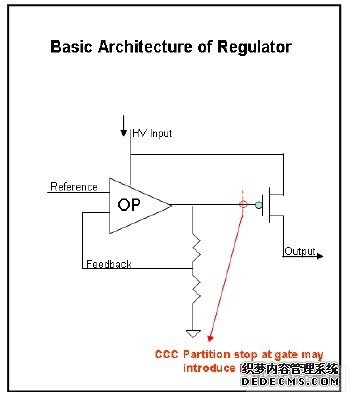

在所有子块中,电压调节器(VR)应有最高精度,由于这些功能块拥有最复杂反馈架构;标准CCC分区方法不能实现电路的正确分区,那时要使用“SPICE”模式来约束分区;大型计算矩阵是基于整个功能块而创建,可确保有效性和精确性。

首先,对于电荷泵、HV开关等子块来说,标准CCC分区已足够好,通过指定它们的设置为“fast2”就可获得精确的仿真结果;其次,对数字子块来说,只需进行逻辑功能检查,因此可使用“hyper3”来节省仿真时间;最后,将整个高压系统中未专门指定的子块的精度设置为“fast3”。

采用上述设置,只要高精度子块有包含大型计算矩阵,从而不仅避免了整个系统创建一个大型矩阵,而且使得我们仍能拥有充足仿真性能和速度。

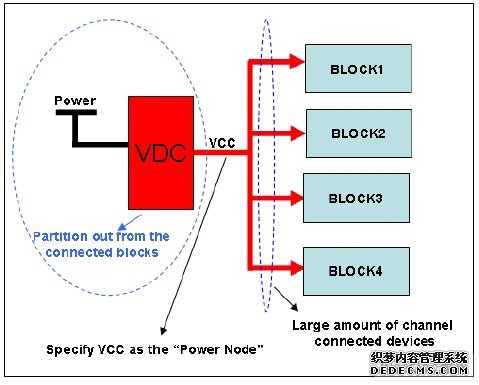

“功率节点”选项帮助进行分区 事实上,三种分区方法用于全芯片仿真还是不够有效。因此除此之外,Magma FINESIM还提供了一个“电源节点”(Power Node)选项。采用这个选项,用户可“告诉”Magma FINESIM如何通过指定“电源节点”来完成电路的分区,这意味着我们能根据电路的函数和属性手工进行电路分区。

如图7所示,当一个节点成为一个被大量器件连接的通道时,我们可将这个节点指定为“电源节点”。完成指定后,这个“电源节点”天生器功能块就可与之后连接的器件分离开来。当然在其之后连接的器件也可进行适当的分区。“电源节点”天生器功能块和之后连接的器件间事件驱动式计算足以确保仿真的有效性。

我们发现最好在电路架构类似如下动作时指定“电源节点”,包括电源天生器或调节器、共源共漏驱动器以及开关功能块,向与器件连接的大量通道提供开关电压。

此外,我们还应频繁检查FINESIM日志文件;若发现最大型分区器件数目不公道且仿真时间太长,那么最好继续进行分区。

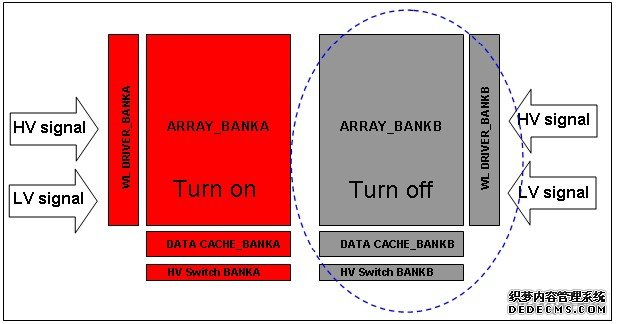

忽略“封闭的”功能块 有时在仿真中,整个仿真过程中总有功能块是封闭的。这种功能块的负载对整个仿真结果几乎没什么影响。因此我们可使用Magma FINESIM_IGNORE选项来忽略这种功能块,节省仿真时间。

例如:在NAND闪存芯片中,阵列可被二等分为两个完全相同部分。有时在仿真中会只启用其中一部分而封闭另一部分。因此在仿真设置中,我们可采用FINESIM_IGNORE来忽略封闭的部分。这个选项如下:

OPTION FINESIM_IGNORE=”ARRAR_BANKB”

OPTION FINESIM_IGNORE=”DATA_CACHE_BANKB”

OPTION FINESIM_IGNORE=”HV_SWITCH_BANKB”

OPTION FINESIM_IGNORE=”WL_DRIVER_BANKB”

使用这个选项来跳过大量器件。

公道RC降低 在一些仿真中,提取的RC网络会被提供给关键功能块。这样就可基于版图提取功能,将大量寄生电阻器和电容器插进网表中。在这些寄生装置中,小型电阻器和电容器将占用大量的Magma FINESIM计算资源,而且对仿真精度起不到什么改善作用。

采用Magma FINSIM_SPFTC选项来指定RC网络。通过指定截止频率值,小于这个值的RC组件将被忽略不计。事实证实,这的确是处理这类网表的一个好方法。

.option FINESIM_SPFTC=1P

使用Verilog-A模型来描述闪存单元 由于Magma FINSIM支持Verilog-A模型,因此我们能使用Verilog-A来描述闪存单元,用它观察闪存单元上高压操纵十分便利。我们会发现几次编程脉冲(program pulses)后单元电压就进步以及几次擦除脉冲(erase pulses)后单元电压就会降低。

Magma FINESIM具有自动替换那些重复定义的子电路(subckt)定义的功能。只要在测试基准中加进Verilog-A模型即可替换MOS级子电路定义,真的十分便捷。

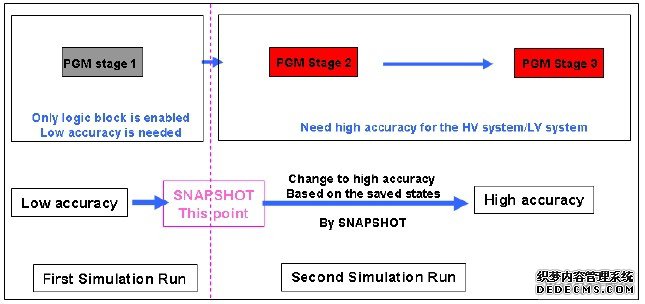

不同操纵期使用不同精度设置 通常在NAND闪存的操纵中,依次会有几个不同时期;不同时期,精度要求也有所不同。因此我们可通过SNAPSHOT 选项,依据仿真中不同时期的需求来设置不同时期的精度。

图6: HV调节器基本架构

例如:在PROGRAM操纵中,它能被分为几个阶段。每个阶段依据功能块操纵和行为会有不同精度设置。第1阶段,精度要求低,只有一些数字块在工作,因此可将芯片精度设置为“低”并开始首次运行。第1阶段仿真结束后,我们可先停止仿真并停在SNAPSHOT这时点以获得RUN_1.SNAPSHOT文件;接着,将精度设置为“高”并重新加载RUN_1.SNAPSHOT文件继续运行仿真。采用这个方法将能够大大节省仿真时间。

图7 “功率节点”指定

多CPU功能 Magma FINESIM提供的多CPU仿真功能是我们要特别夸大的最后一个方法。它意味着我们能够同时采用2个或几个CPU来运行仿真。只要CPU资源充分,这项功能就可明显改善仿真性能。

图8 忽略封闭的功能块

仿真性能比较

在本章中,通过运行Magma FINESIM与另一款Fast SPICE工具进行比较得到了一些数据。由于PROGRAM操纵中多数功能块都是打开的,因此此次我们采用一次标准PROGRAM操来作为测试案例。

图9 不同时期设置不同精度

4.1 简单仿真精度比较

采用了3个有高精度要求的关键DC电压信号作为测试点。

数据显示:FINESIM的精度与另一款Fast SPICE工具不相上下。

4.2 仿真时间比效

仿真时间结果是如此令人欢欣鼓舞,采用4CPU的方式几乎节省了40%仿真时间。

总结

尽管大型混合信号芯片仿真是对今天 Fast SPICE工具的一项挑战。但Magma FINSIM却能有效处理NAND闪存芯片的仿真。只要进行适当仔细的设置,它就可很好执行仿真;特别是拥有了良好电路分区和多CPU功能,仿真性能更可得到大幅改善。 (美光半导体上海设计中心 )

- 上一篇:共享单车智能锁方案 共享单车技术方案 下一篇:主板上声卡芯片介绍

QQ在线客服

QQ在线客服